- Товари

- Оценочные и отладочные платы на основе микроконтроллера

- Terasic DE0-Nano, Отладочная плата на базе FPGA Altera Cyclone IV ...

Terasic DE0-Nano, Отладочная плата на базе FPGA Altera Cyclone IV ...

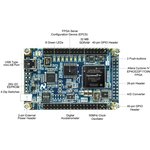

DE0-Nano – малогабаритная отладочная плата на базе FPGA Altera Cyclone IVEP4CE22F17. Функциональные возможности платы могут быть расширены посредством дочерних плат: LTM (дисплейный модуль с TFTLCD4,3”), THDB-ADA (модуль со скоростными АЦП и ЦАП), D5M (модуль видеокамеры 5 Мпикселей) или плат пользователя.

Отличительные особенности:

• установленная FPGA Cyclone® IV EP4CE22F17C6N: 22,320 логических элементов (LE), 594 кбит встроенной памяти, 66 перемножителей 18 x18, 4 PLL общего пользования, 153 I/O;

• интегрированный USB-загрузчик;

• установленная конфигурационная память EPCS16;

• два соединителя по 40 выводов для подключения плат функционального расширения (LTM, THDB-ADA, D5M) или плат пользователя;

• по 2 вывода источников питания + 5 В и +3,3 В;

• соединитель на 26 выводов: 16 цифровых I/O, 8 аналоговых входов;

• установленная SDRAM32 МБ;

• 2 кБ I2C EEPROM;

• периферия пользователя: 8 светодиодов, две бездребезговые кнопки, 4 dip переключателя, трёхосевой акселерометр ADXL345;

• 8-канальный АЦП NSС ADC128S022, 12-разрядный до 200 ksps;

• осциллятор 50 МГц;

• USB разъем (загрузчик, питание).

Комплектация:

• отладочная плата DE0-Nano;

• USB кабель.

| Серия оценочной/отладочной платы | cpld/fpga |

| Ядро базового компонента | Altera |

| Наименование базового компонента | ivep4ce22f17 |

| Наличие USB интерфейса | да |

| Наличие установленного (в комплекте) дисплея | нет |

| Наличие макетной области | нет |